## Available online www.jsaer.com

Journal of Scientific and Engineering Research, 2020, 7(8):230-234

**Research Article**

ISSN: 2394-2630

**CODEN(USA): JSERBR**

# **DRAM System Power Supply and Energy Saving Techniques**

### Apoorva Reddy Proddutoori

San Diego

Email ID: apoorvaproddutoori@gmail.com

Abstract According to this paper, measure is one of the principal wellsprings of energy utilization in PC frameworks. Accordingly, lessening the energy utilization of Measure can draw out the lifetime of battery worked implanted/versatile frameworks. Even though prefetching plans have generally been utilized to further develop the framework execution, using them for the energy preservation of Measure still can't seem to be researched. For such energy preservation, our plan precisely predicts, and groups potential future Measure gets to. Bunched Measure gets to take advantage of a famous first prepared the early bird gets the worm memory demand booking and a shutdown method of Measure more actually; the likelihood of line cushion hits and inactive periods is fundamentally expanded by the paper. Thus, a lot of column enactment and inactive energy utilization, which are significant energy utilization factors in present day Measure, can be saved.

**Keywords** measure, power, memory, energy efficiency, throughput, supply

#### Introduction

The most bizarre memory applications are partitioned into two gatherings. Installed applications like the code stockpiling for PCs and cell phones for the most part require quick arbitrary read activities. Mass memory utilization applications such as the stockpiling component of advanced cameras and memory cards are fulfilled by generally sluggish irregular read admittance time. As of late, a few blaze memory cell models including staggered cell innovation are distributed and popularized. Among them, the NAND-type streak memory has been known as a compelling glimmer memory for mass capacity applications where minimal expense is more basic than the quick irregular access time. The little cell size of the NAND-type streak memory comes from its one-of-a-kind NAND string cell structure. The gadget portrayed in this paper is focused on to be utilized in implanted applications which require high velocity arbitrary read activity. The gadget utilizes a NAND-type streak memory cell to maintain the upside of little cell size. To accomplish a quicker irregular, peruse access time and rapid program activity with the NAND streak cell, a progressive line decoder and a collapsed piece line conspire are utilized.

Power and energy consumed by primary memory frameworks in server farm servers have expanded as the Measure limit and data transmission increment. Especially, foundation power represents an impressive part of the complete Measure power utilization; the part will increment further sooner rather than later, particularly when dialing back innovation scaling drives us to give important Measure limit through connecting more Measure modules or stacking more Measure contributes a Measure bundle. Albeit current Measure design upholds low power states at rank granularity that mood killer a few parts during inactive periods, strategies to take advantage of memory-level parallelism make the position granularity power state become insufficient. Moreover, the long wake-up inertness is one of deterrents to embracing forceful power the board (PM) with profound shut down states.

In versatile plan, a worry for power utilization is a significant issue. Portable applications consume more power by handling progressively convoluted undertakings at higher speed with a limitation of restricted batteries. All things considered; portable applications are supposed to have broad battery duration. Another conceivable method for expanding battery duration is to decrease the reserve power utilization. The on-chip ECC strikingly brings down the backup power utilization by diminishing oneself revive current which is then applied to the instance of the auto invigorate.

#### **Understanding Dram Architecture**

DDR memory is turning out to be all the more broadly utilized because nearly all applications requiring quick handling of tremendous measure of information - PCs, waiters, gaming consoles, card scanner, compact shopper gadgets for instance - rely upon the quick admittance to, and accessibility of, a lot of high data transmission Smash. Its qualities permit unstable data to be held and can be accessed in a quicker and more straightforward way which is basic for giga speed networks and productivity that are requested by PC frameworks today.

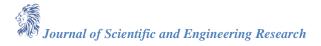

Figure 1: DRAM Memory Division

These elements and power utilization benefits make them especially suitable for use in scratch pad PCs, waiters, and low power mobile applications. The principal distinction among SDRAM and the current in-use of DDR SDRAM are:

- [1]. Power supply voltage

- [2]. Interface

- [3]. Information move Recurrence

The circuit scale develops, static timing investigation (STA) turns into a normal way to deal with confirm timing requirements, or rather it is dog recently the best way to perform full-chip timing investigation. In static timing investigation, we engender the most recent appearance time and change time all through a circuit and infer the longest shortest way delays. CMOS circuits comprise of CMOS doors and interconnects, what's more, presently postpone seasons of each part, for example the entryway spread delay and the interconnect proliferation delay, are independently calculated. Concerning interconnect delay, it is notable or then again other comparative strategies can appraise exact progress wave structures proliferating through straight gadget organizations. On the other hand, CMOS doors are non-direct gadgets and the assessment of door delay is intrinsically more confounded.

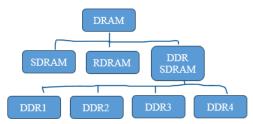

Figure 2: Memory Allocation

In picking a decent DDR power supply, one should gauge the expenses with exhibitions as well as other specialized necessities like info voltages or result flows. Accepting that the electrical particular is as of now fixed, the decisions of DDR Powers IC's are principally weighted on the accompanying variables:

- [1]. What power change productivity could the DDR at any point supply IC proposition? Most sellers give productivity no less than 90% or more. Higher productivity means less misfortune and would mean an extraordinary arrangement to valuable influence sources coming from batteries in compact items.

- [2]. Is the exchanging recurrence adequately high? Higher recurrence implies more modest worth outside inductor and capacitors can be utilized and would be more modest in size.

- [3]. Does the stock IC gives sink and source capacity and voltage following element that are particulars to drive DDR memory?

- [4]. Bundle size of the chip plays a significant element to space compelled applications like compact customer items.

- [5]. Are there broad controls and interact that can offer the fashioner the adaptability of many control and security capabilities? This would take into consideration simple execution of intricate plans.

In any case, the expansion in dynamic current can be limited by taking out section overt repetitiveness and by keeping the inward stock voltage level as low as the determination permits, hence, autonomous of the outside voltage variety. The brought down interior voltage, regardless of whether it might dial back the activity speed, is sufficient to accomplish DDR.

#### **Implementation**

Thusly, delay calculation in light of look-into tables is generally utilized is approach generally requires an earlier portrayal cycle to construct look-into tables utilizing a circuit test system. Because of the constraint of circuit reproduction costs, entryway portrayal is normally performed in two-layered space; yield stacking and progress season of input waveform (slant). The boundary of slant plans to catch the impact of waveform shape on door delay. Recently many elements make. progress waveforms more refrain in nanometer advances, for example, crosstalk clamor, between interface inductance and resistive safeguarding, and consequently catching waveform shape by utilizing a solitary boundary of incline is getting harder. By and by, the quantity of boundaries to communicate wave structure shapes doesn't expand on account of entryway portrayal.

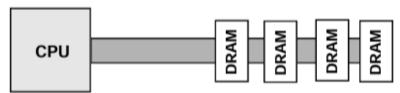

Figure 3: SDRAM Protocal

#### A. Effects of Dynamic Voltage Scaling

The insusceptibility of the DVS for grouped segment disappointments makes segment overt repetitiveness superfluous. The section overt repetitiveness added to ECC plans causes an additional increment in region which brings down the quantity of securing passes on. On the other hand, the DVS without section overt repetitiveness can be flopped by the increment of grouped segment disappointments. The DVS without section overt repetitiveness is demonstrated, by the assessment, to be more financial answer for grouped section disappointments than the customary ECC with segment overt repetitiveness. Gotten from the quantity of grouped segment disappointments, Fig. 2 shows the correlation between the revision likelihood of the DVS without section overt repetitiveness and the standardized procurement pass on from the customary ECC with section overt repetitiveness. The amendment likelihood is determined with Poisson appropriation, and the way of behaving of the standardized securing pass on is analogized out of a few assessed information.

#### B. Power and Energy

While regular NAND streak recollections have 16 cells per NAND string and they use stringbased block eradicate, the gadget in this paper has eight cells for every string setup furthermore, it utilizes word-line-based delete. At this point when the word-line-based eradicate is rehashed in a string, the phone upset condition becomes much more terrible than the string-based delete. Utilizing eight cells for each string and self-helping strategy with siphoned piece line plot definitely lessens program upset as displayed. Vpass in this plot is the voltage applied to deselected word-lines in a chose string during page program activity. Since the voltage distinction between the drifting door also, the channel, causing the upset, is decreased as Vpass is expanded during self-supporting activity, the edge voltage shift of a program restrained cell on the chose word-line is decreased as Vpass increments when Vpass is moderately huge. In any case, this isn't correct when Vpass is sufficiently little to prompt a neighborhood self-helping peculiarity.

The edge voltage shift from the eradicated state (V) is practically insignificant analyzed with that of a traditional plan. The unsettling influence to currently modified cells is a lot more modest than eradicate cells because of a more modest electric field between the drifting entryway and the channel. At the point when a chose bit-line is set to 4.5 V, the upset electric field on deselected word-line cells is tiny in light of the fact that the channel voltage is likewise self-helped. For this situation, the voltage distinction between the drifting entryway what's more, the channel, causing the upset, is straightforwardly corresponding to Vpass, and it is free of the quantity of cells in a string. As needs be, the limit voltage shift of deselected word-line cells in a chose string increments as Vpass increments. Taking into account that the most extreme limit voltage of a deleted cell being perceived as a delete state is intended to be 1 V, delete cycles up to 10 for each NAND string can be performed by setting the Vpass voltage underneath 9.8 V. The base Vpass not set in stone by the greatest modified cell which still up in the air by the venturing voltage also, optional impacts, for example, commotion and information design put away in a NAND string.

#### Conclusion

A huge collection of work on the decrease of the power also, energy utilization of Measure has been collected. A larger part of such investigations has pointed toward diminishing the BG energy utilization, including the energy utilizations of standing by and reviving. A few works have proposed lessening the inactive energy utilization by taking advantage of the low-power methods of Measure. The vital commitment of these plans is to stretch the Measure inactive periods to take advantage of the low-power modes for a more drawn-out timeframe. Notwithstanding, the framework execution is essentially debased on the grounds that ordinary memory gets to are conceded or moved into specific positions or chips to have a more drawn-out time of inactive time. Although the power utilization from Measure sitting can be decreased, the energy saving might be offset even declined. If the framework runtime increments. Late investigations have zeroed in on the over fetch issue of current Measure structures. A few examinations have explored alleviating the enormous line actuation cost and lessening the squandered energy utilization brought about by late Measure architectures utilizing a sub rank setting, which is the revamping of an ordinary Measure framework into a more modest gathering of Measure chips to permit less Measure chips to be associated with the Measure gets to and parceling the Measure stockpiling cluster into a few subarrays to initiate less piece lines for Measure. The far-reaching tradeoffs from the utilization of a subrank framework including demand booking and blunder security systems were researched in. In these plans, the position subsetting expands the intricacy of the Measure association and blunder insurance techniques inferable from an information design change between a last-level store and the

Measure chips. Dissimilar to rank subsetting plans, a Measure compose access disposal plot that takes advantage of a restricted worth and quiet stores attributes was proposed to lessen the huge column enactment cost without the requirement for changing the Measure framework association and engineering. Our proposed conspire, Applaud, addresses the two significant power and energy utilization variables of Measure portrayed above. Applaud stretches the Measure standing by periods to lessen the inactive energy utilization and builds the Measure line support hits to lessen the initiation energy utilization using prefetching-based memory traffic grouping components.

#### References

- [1]. Seung-Jun Bae, Kwang-Il Park, Jeong-Don Ihm, Ho-Young Song, Woo-Jin Lee, Hyun-Jin Kim, Kyoung-Ho Kim, Yoon-Sik Park, Min-Sang Park, Hong-Kyong Lee, Sam-Young Bang, Gil-Shin Moon, Seok-Won Hwang, Young-Chul Cho, Sang-Jun Hwang, Dae-Hyun Kim, Ji-Hoon Lim, Jae-Sung Kim, Sung-Hoon Kim, Seong-Jin Jang, Joo Sun Choi, Young-Hyun Jun, Kinam Kim, "An 80 nm 4 Gb/s/pin 32 bit 512 Mb GDDR4 Graphics DRAM With Low Power and Low Noise Data Bus Inversion", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 1, JANUARY 2008

- [2]. Saeng-Hwan Kim, Won-Oh Lee, Jung-Ho Kim, Seong-Seop Lee, Sun-Young Hwang, Chang-Il Kim, Tae-Woo Kwon, Bong-Seok Han, Sung-Kwon Cho, Dae-Hui Kim, Jae-Keun Hong, Min-Yung Lee, Sung-Wook Yin, Hyeon-Gon Kim, Jin-Hong Ahn, Yong-Tark Kim, Yo-Hwan Koh, and Joong-Sik Kih, "A Low Power and Highly Reliable 400Mbps Mobile DDR SDRAM with On-Chip Distributed ECC", IEEE Asian Solid-State Circuits Conference, Nov 2007

- [3]. Kyung-Soo Ha, Chang-Kyo Lee, Dongkeon Lee, Daesik Moon, Hyong-Ryol Hwang, Dukha Park, Young-Hwa Kim, Young Hoon Son, Byongwook Na, Seungseob Lee, Youn-Sik Park, Hyuck-Joon Kwon, Tae-Young Oh, Young-Soo Sohn, Seung-Jun Bae, Kwang-Il Park, and Jung-Bae Lee, "A 7.5 Gb/s/pin 8-Gb LPDDR5 SDRAM With Various High-Speed and Low-Power Techniques", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 55, NO. 1, JANUARY 2020

- [4]. Tae-Sung Jung, Member, IEEE, Do-Chan Choi, Sung-Hee Cho, Myong-Jae Kim, Seung-Keun Lee, Byung-Soon Choi, Jin-Sun Yum, San-Hong Kim, Dong-Gi Lee, Jong-Chang Son, Myung-Sik Yong, Heung-Kwun Oh, Sung-Bu Jun, Woung-Moo Lee, Ejaz Haq, Kang-Deog Suh, Syed B. Ali, and Hyung-Kyu Lim, "A 3.3-V Single Power Supply 16-Mb Nonvolatile Virtual DRAM Using a NAND Flash Memory Technology", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 11, NOVEMBER 1997

- [5]. Yebin Lee and Soontae Kim, "CLAP: Clustered Look-Ahead Prefetching for Energy-Efficient DRAM System", IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 24, NO. 5, MAY 2016

- [6]. Chang-Kyo Lee, Junha Lee, Ki-Ho Kim, Jin-Seok Heo, Gil-Hoon Cha, Jin-Hyeok Baek, Dae-Sik Moon, Yoon-Joo Eom, Tae-Sung Kim, Hyunyoon Cho, Younghoon Son, Seonghwan Kim, Jong-Wook Park, Sewon Eom, Si-Hyeong Cho, Young-Ryeol Choi, Seungseob Lee, Kyoung-Soo Ha, Youngseok Kim, Bo-Tak Lim, Dae-Hee Jung, Eungsung Seo, Kyoung-Ho Kim, Yoon-Gyu Song, Youn-Sik Park, Tae-Young Oh, Seung-Jun Bae, In-Dal Song, Seok-Hun Hyun, Joon- Young Park, Hyuck-Joon Kwon, Young-Soo

- Sohn, Jung-Hwan Choi, Kwang-Il Park, Seong-Jin Jang, "Dual-Loop 2-step ZQ Calibration for Dedicated Power Supply Voltage in LPDDR4 SDRAM", IEEE Asian Solid-State Circuits Conference, Nov 2017

- [7]. Seunghak Lee, Nam Sung Kim, and Daehoon Kim, "Exploiting OS-Level Memory Offlining for DRAM Power Management", IEEE COMPUTER ARCHITECTURE LETTERS, VOL. 18, NO. 2, JULY-DECEMBER 2019

- [8]. Bruce Jacob and David Wang, "DRAM: Architectures, Interfaces, and Systems A Tutorial", ISCA 2002

- [9]. https://semiengineering.com/knowledge\_centers/memory/volatile-memory/dynamic-random-access-memory/

- [10]. https://www.simms.co.uk/tech-talk/understanding-dram-dynamic-random-access-memory/

- [11]. https://www.embedded.com/choosing-the-right-power-supply-ics-for-your-ddr-memory-subsystem/