Journal of Scientific and Engineering Research, 2019, 6(11):311-314

**Research Article**

ISSN: 2394-2630 CODEN(USA): JSERBR

# Improvizing Power Optimizations Using Dynamic Cascode Voltage Switching Logic

# Apoorva Reddy Proddutoori

San Diego

# Email: apoorvaproddutoori@gmail.com

Abstract In this paper we display another choice the 13-decision demonstrate, based on a graph chart that can be utilized to maximize proficiency Make DCVS circuits yourself. We assess our compared to customary DCVS amalgamation strategies that utilize requested parallel choices graphs that illustrate that our approach will without a doubt succeed as well as or on the other hand superior compared to OBDD based methodologies. Within the journey for high-performance CMOS, dynamic cascode voltage switch (DCVS) circuits are rising as an vital modern range of ponder. consolidated circuits Potential benefits are higher circuit thickness and speed and lower control dispersal. In this paper we show another choice the 13-choice graph, a diagram-based demonstrate that can be utilized to rapidly synthesize DCVS circuits. We differentiate our technique with DCVS mix strategies based on diminished requested twofold choice charts and illustrate that our strategy will continuously outflank standard based procedures. Changes on benchmark circuits run from to ~50 percent, with an normal enhancement of major percent.

## Keywords power analysis, power, DCVS, voltage drop, CMOS,

## 1. Introduction

Numerous performance improvements have been made. CMOS devices have been shrinking in size over the past few decades. However, the problem of noise effects, which can cause significant errors during circuit operation, becomes critical. Furthermore, as explained in, noise does not decrease proportionally with the supply voltage, so a drop in the supply voltage reduces the noise immunity of the circuit.

To maintain performance, guard band voltages must be used. Therefore, extensive and relevant research has been conducted on noise tolerant circuits. The design of noise tolerant circuits has received increasing attention. The most commonly used strategy to achieve low power configurations is to lower the supply voltage Vdd. However, for performance reasons, the threshold voltage Vt must remain constant and must be lowered to the point where the overload (Vdd-Vt) is still large enough. As Vt is lowered, there is an initial exponential increase in the subthreshold leakage current. As Vdd and Vt are lowered, the increase in leakage power can start to dominate the dynamic switching performance. A dual-channel dynamic cascode voltage switch (DCVS) logic rail CMOS scheme. It outperforms conventional logic single rail techniques in terms of circuit delay, space requirements, and logic adaptability. Another advantage of DCVS circuits is their ease of construction: single gate delays for complex differential logic functions using simple methods beyond the simple K map-based strategy. The logic capabilities are also synthesizable.

Although DCVS static circuits may require more power, they outperform conventional CMOS circuits due to their turn-on and discharge times that depend on the turn-off paths of the DCVS tree, which are usually not balanced. The asymmetry increases the duration of the transient state while current flows through the DCVS circuit latch, increasing power dissipation.

However, performance usage may be an issue in low performance applications. In the following sections, the low voltage CMOS DCVS logic circuit built using the K-map method is first presented, followed by implementation and analysis.

#### 2. Effort of Implementation

First, DCVS tree amalgamation is getting to be a critical modern inquire about course within the mission for first class execution, tall capability CMOS coordinates circuits. There are two primary components in DCVS circuits:

- i. a stack circuit

- ii. an n-transistors

arrange, which carry out a specific Boolean work. The structure of the organize is such that for in case the hub f4 is, at that point each input vector separated from ground, at that point, at that point, f(f) is associated to the ground through a particular course. An outline of a DCVS circuit can be found in 1. Figure Since arbitrariness is the nature of clamor, the previously mentioned referenced strategies are troublesome to achieve effective circuit immunity. As a result, many novel procedures based on probabilistic speculation. The PCMOS, or probabilistic CMOS, An prior endeavor to require advantage of the irregular nature of the CMOS contraptions to induce more arrange space, in any case The foremost critical parts of the whole computation must stay right and encourage examination of commotion resistance to the method of reasoning entryway can't be remained absent from in this work. Asked twofold choice charts have been utilized broadly within the writing for analyzing and synthesizing different rationale circuits. OBDDs can be streamlined to a decreased canonic structure — the twofold choice chart with decreased arrange. ROBDDs can moreover be supportive. for multilevel optimization and plan confirmation. There are a number of DCVS tree plan calculations, counting those utilizing ROBDDs ROBDD-based calculations by and expansive incorporate re- duction of "totally amplified" OBDDs. An outline of the over algorithm's flowchart for choosing which Figure portrays gadgets which will be classified as low-Vt gadgets. 4. The stacking of the design circuits kicks off the method. At that point, the control parameters must be entered. To wrap up the initialization- gadget bunch, gadget block, prepare, and key word are made. The procedure enters a handling circle at this point. which tests each setup in gathering. A test is set up. not totally set in stone expecting that the ongoing design passes the standards.

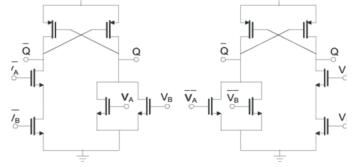

Figure 1: Mux based DCVS Algorithm

In case not, the method goes back in time to discover the another arrangement. to be tried proportion. In case the current setup passes the rules, a test is made to choose whether the continuous plan moreover passes the models. Simulation determines this, delay rules, a inactive clock, and get to a database of other properties. In the event that not, the method rehashes itself to find the following setup that will be evaluated. On the off chance that the current setup is passes the models, get to is once more made to choose the finest plan. If no ideal setup is found, the method returns in a loop to recover the taking after arrangement. tried. At the point when the finest course of action is found, it is surrender as the most excellent arrangement.

## 3. Algorithm Analysis A. DCVS Logic Insertion

The DCVS contrive shown in Fig.1 moreover have commotion insusceptibility affect since of its differential action. So, in arrange to We incorporate this to compensate for the misfortune of insusceptibility in DCVS CMOS into the circuit, coming about in an moved forward noise-tolerant arrange as portrayed in Figure. The result the DCVS CMOS Logic is pushed into the ordinary NAND Door, the differential yield together with its rearranged flag are related with the Feedback Circle which comes about a mixed circuit plot based on the DCVS strategy and chart.

#### **B. Decision Diagram**

The method of blend for decision diagram is top-down. which advances one level at a time. At each level, the reasonable alter rules are connected. After all center points at a given level are expanded to next level after it has been handled, the ensuing level, which is taken care of within the same way. The amalgamation strategy closes when each one of the center points at the continuous level are terminal hubs. A diagram of the amalgamation in its aggregate Figure 2 portrays the method of decision. The sum of presented extra gadgets for an The substitution rule's application is less than or more prominent than or break even with to d-1, in the event that the common predecessor center N is d levels over the continuous level. The number of gadgets saved at the progressing level is 2. We will add the confinement that the The substitution run the show will as it were be utilized in the event that the The common predecessor isn't more than three levels over current point. This confinement ensures that add up to number of presented gadgets levels for each substitution application run the show will continually be not precisely or proportionate to that of the relating OBDD show.

In any case, to keep the multifaceted nature of a CS-based video encoder be moo, an uncommon trademark is that CS can "clearly" capture pressed video data without momentarily putting absent the rough data. As a result, without get to the crude information, it is challenging to execute estimation rate assignment precisely for each square. The compressive video detecting framework, in which each square is decided to be either meager or non-sparse by foreseeing the sparsity based on the past reference outline (or key outline) that has been expectedly or completely tested and changed utilizing the block-based discrete cosine change, as it were ambiguously said this issue to our information. Whereas each non-sparse piece is completely inspected, compressive inspecting is utilized for inadequate pieces. This approach has two major downsides:

- i. it must bolster a completely inspected reference outline on a normal premise, which requires transiently putting away the crude information and performing a few change, both of which go against the initial expectation of CS-based information compression and are contradictory with the CS-based single-pixel camera

- ii. the estimation rate allotment is too harsh to distribute either a particular rate or the complete rate for each piece.

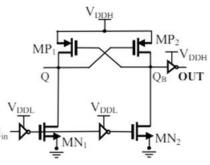

Figure 2: Traditional Level Converter

In spite of the way that level converter likewise consumes power, any formal approach to the formulation of the use of For circuit design, dual supply voltages most likely take the delay and the amount of power used into account. In other words, the level transformation should be achieved by negligible deferral and lower power utilization to accomplish high execution CMOS circuits. Additionally, a structure like as "VDDH circuit, VDDL circuit, VDDL circuit, VDDH circuit" circuit..." require the addition of numerous level converters at each interface "VDDL circuit - VDDH circuit". Consequently both bringing down the power consumed in the level

converter and As a result, reducing the number of level converters becomes crucial concern when using dual supply voltages. Care has been taken to configuration level converter precisely for bringing down consumption of power and delay in propagation without corrupting execution.

# 4. Conclusion

The correct DCVS tree configuration's logic behavior The outcomes of the simulations support ration. The gadget model boundaries utilized depend on multi-Vt CMOS technology in bulk The delay, current leakage, and switch power reproduction results for common DCVS circuits are summarized, with and without mixed-Vt devices. In this paper a novel CMOS TSPC adiabatic DCVS rationale circuit with the Low-power VLSI technique has been reported. By means of pass transistors and The TSPC scheme has compensated transistors by been obtained for simplicity's sake. Utilizing the capacitance coupling from the bootstrap this PC adiabatic DCVS transistor logic circuit made using the adiabatic method uses minimal percent less energy than the one that uses a CAL (clocked adiabatic latch) approach. Likewise there is a reduction in the proposed rising and falling times level converters when contrasted with customary plans. However, simulation results demonstrate that the suggested designs have recorded less propagation delay and noise, contrasted with past plans.

# References

- [1]. N. Kanopoulos, Dimitris Pantzartis, and Frederick R. Bartram, "Design of Self-Checking Circuits Using DCVS Logic: A Case Study", IEEE, 1992

- [2]. Xinghua Yang, Fei Qiao, Qi Wei, Huazhong Yang, "A General Scheme for Noise-Tolerant Logic Design Based on Probabilistic and DCVS Approaches", IEEE, August 2015

- [3]. A. Jaekel, "A New Model for Constructing DCVS Trees", IEEE, 1997

- [4]. W. Chen, W. Hwang, P. Kudva, G.D. Gristede, S. Kosonocky and R.V.Joshi, "M i xed M u It i -T h res h o I d Differentia I Cascod e Vo I t ag e Switch (NIT- DCVS) Circuit Styles and Strategies for Low Power VLSI Design", IEEE, 2001

- [5]. H. P. Chen and J. B. Kuo, "A 0.8V CMOS TSPC Adiabatic DCVS Logic Circuit with the Bootstrap Technique for Low-Power VLSI", IEEE, May 2004

- [6]. A. Jaekel, "A decision-diagram-based synthesis procedure for DCVS circuits", Can. J. Elect. & Comp. Eng., Vol. 23, No. 4, October 1998

- [7]. Hung-Wei Chen, Li-Wei Kang, Chun-Shien Lu\*,

" Dynamic measurement rate allocation for distributed compressive video sensing", Research Gate, July 2010

- [8]. Jaroslav Koton, "International Journal of Advances in Telecommunications Electrotechnics, Signals and Systems", Vol. 2, No. 3, 2013