Journal of Scientific and Engineering Research, 2016, 3(2):284-290

**Research Article**

ISSN: 2394-2630 CODEN(USA): JSERBR

# Advanced Digital System Design with Verilog: From Basics to High-Speed Applications

# Iqtiar Md Siddique

Department of Computer Engineering, RMIT University, Australia. Email: iqtiar.siddique@gmail.com

Abstract This Papers offers a comprehensive exploration of digital design, blending foundational concepts with advanced techniques to address modern high-speed applications. This paper begins with an introduction to digital logic design, offering clear explanations of basic concepts such as Boolean algebra, combinational and sequential circuits, and timing analysis. It then delves into the Verilog hardware description language, guiding readers through essential coding practices and simulation strategies. As the content progresses, more complex topics are introduced, including design optimization, power management, and high-speed design techniques. The research also covers critical aspects of digital system design, such as timing closure, signal integrity, and verification methodologies, ensuring robust and reliable implementations. Numerous examples, practical systems. This research is an invaluable resource for students, engineers, and professionals looking to enhance their knowledge and skills in digital system design, enabling them to tackle the challenges of modern electronic design with confidence.

### Keywords Synthesis, Sequential, Combinational Logic, Verilog, Timing Analysis

## 1. Introduction

Advanced Digital System Design with Verilog: From Basics to High-Speed Applications is a comprehensive guide that bridges the gap between fundamental digital design concepts and the demands of modern high-speed applications. As digital systems become increasingly complex and pervasive in our daily lives, a deep understanding of both the underlying principles and advanced techniques is crucial for engineers, designers, and students alike. This book is crafted to serve as both a foundational textbook for beginners and a detailed reference for seasoned professionals looking to refine their skills in digital design using Verilog, one of the most widely used hardware description languages (HDLs) in the industry. The importance of digital system design has grown exponentially with the rapid advancement of technology. From consumer electronics and telecommunications to automotive systems and aerospace applications, digital systems form the backbone of numerous critical applications. The demand for faster, more efficient, and reliable digital systems continues to drive innovation in design methodologies, tools, and technologies. This book aims to provide readers with the knowledge and tools necessary to meet these demands, focusing on high-speed applications where performance and reliability are paramount.

This research begins with an introduction to digital logic design, laying a strong foundation in the basics of Boolean algebra, logic gates, combinational and sequential circuits, and timing analysis. These topics are essential for understanding the fundamental building blocks of digital systems. The early chapters are designed to be accessible to readers with little or no prior experience in digital design, providing clear explanations and numerous examples to help build a solid understanding. As the reader progresses through the book, they will be introduced to Verilog, a powerful and versatile hardware description language that is widely used for designing

and modeling digital systems. Verilog allows designers to describe complex digital circuits at various levels of abstraction, from high-level behavioral descriptions to detailed gate-level implementations. The book covers the syntax and semantics of Verilog in detail, along with best practices for writing efficient and maintainable code. Readers will learn how to use Verilog for designing combinational and sequential circuits, as well as for simulating and verifying their designs.

In addition to the basics of digital logic and Verilog, the book delves into more advanced topics that are critical for high-speed digital system design. These include design optimization techniques, such as pipelining and parallelism, which are essential for achieving high performance in modern digital systems. The book also covers power management strategies, which are increasingly important in an era where energy efficiency is a key concern in electronic design. One of the unique features of this book is its focus on high-speed design techniques. High-speed digital systems, such as those used in networking, telecommunications, and computing, require careful attention to timing, signal integrity, and power consumption. The book explores these challenges in depth, providing readers with the knowledge and skills needed to design systems that meet stringent performance requirements. Topics such as timing closure, clock domain crossing, and signal integrity are covered in detail, along with practical guidelines for addressing these challenges in real-world designs.

Verification is another critical aspect of digital system design, and this book provides a thorough introduction to modern verification methodologies. Readers will learn how to use Verilog for writing testbenches and conducting simulations to verify the correctness of their designs. The book also introduces advanced verification techniques, such as formal verification and hardware-in-the-loop simulation, which are essential for ensuring the reliability of complex digital systems. Throughout the book, the concepts and techniques are illustrated with numerous examples, practical exercises, and real-world case studies. These examples provide readers with hands-on experience in designing and verifying digital systems, reinforcing the theoretical concepts covered in the text. By the end of the book, readers will have a deep understanding of digital system design with Verilog and will be well-equipped to tackle the challenges of designing high-speed digital systems in today's competitive and rapidly evolving technological landscape.

we have traversed the essential principles of digital logic, explored the intricacies of Verilog, and delved into the complexities of high-speed digital design, ensuring that readers are equipped with the knowledge and skills necessary to meet the demands of modern electronic systems. The journey began with a solid grounding in digital logic design, providing the necessary building blocks for understanding how digital systems operate. This foundation was crucial for enabling readers to grasp more complex concepts as they moved through the book. The introduction to Verilog was presented in a detailed and accessible manner, guiding readers through the syntax, semantics, and best practices for this powerful hardware description language. By mastering Verilog, readers gained the ability to model, design, and simulate digital circuits with precision and efficiency.

The advanced topics covered in the book, including design optimization, power management, and high-speed design techniques, are critical for addressing the challenges of contemporary digital systems. In today's world, where performance, power efficiency, and reliability are paramount, understanding these advanced concepts is essential for any digital system designer. The book's focus on high-speed design, with detailed discussions on timing closure, signal integrity, and verification, equips readers with the tools needed to develop robust, high-performance systems that meet stringent industry requirements.

Verification, a cornerstone of reliable digital system design, was given significant attention, ensuring that readers understand the importance of validating their designs through rigorous testing and simulation. The introduction to modern verification methodologies, including advanced techniques such as formal verification, provided readers with a comprehensive toolkit for ensuring the correctness and reliability of their designs. The practical examples, exercises, and real-world case studies interwoven throughout the book reinforced the theoretical concepts, offering readers hands-on experience in designing and verifying digital systems. These practical elements ensure that the knowledge gained from this book is not just theoretical but also applicable to real-world challenges.

#### 2. Related works

The literature on digital system design using Verilog and related technologies is extensive, reflecting the diverse applications and growing complexity of modern electronic systems. The following review covers key

contributions in this area, highlighting foundational texts and advanced research that inform the design, synthesis, and implementation of digital systems. Palnitkar [1] provides a foundational guide to Verilog HDL, offering a comprehensive introduction to digital design and synthesis. This work is instrumental in understanding the basics of Verilog, making it a critical resource for both novices and experienced designers. Ashenden [2] builds on this foundation by focusing on embedded systems, illustrating how Verilog can be effectively used in the context of embedded digital design. These two texts together form a strong basis for understanding digital design with Verilog. Khan [3] extends the discussion to digital signal processing systems, emphasizing practical approaches in the design process. This book is particularly valuable for designers focused on signal processing applications, offering insights into both the theoretical and practical aspects of digital design. Rafiquzzaman [4] contributes to the understanding of digital logic and microcomputer design, providing a broader context in which Verilog can be applied. This text is essential for those looking to integrate digital logic design principles with microcomputer architecture.

Wilson [5] and Ferdjallah [6] further explore the application of Verilog and VHDL in FPGA design and digital systems modeling, respectively. Wilson's work is particularly notable for its practical recipes for FPGA design, making it an excellent resource for engineers working on FPGA-based projects. Ferdjallah's introduction to digital systems modeling is equally valuable, offering a comprehensive overview of synthesis and simulation using VHDL, which complements the Verilog-based approaches discussed in other texts. Ahmad et al. [7] demonstrate the application of Verilog in designing a digital transmitter for Zigbee applications, showcasing the practical use of Verilog in wireless communication systems. Their work highlights the flexibility and power of Verilog in implementing specific digital communication protocols. Salcic and Smailagic [8] focus on digital systems design and prototyping using field-programmable logic, providing a detailed guide on using hardware description languages for prototyping. This work is crucial for those interested in the early stages of digital system design, where rapid prototyping is essential.

Agrawal and Mishra [9] and Sharawi and Aloi [10] explore high-speed digital design, with the former focusing on UART design and the latter on circuit modeling in high-speed designs. These papers are particularly relevant for engineers working on high-performance systems where speed and timing are critical considerations. Tan and Rosdi [11] provide a survey of Verilog HDL simulator technology, offering insights into the tools and techniques available for simulating Verilog designs. This survey is a valuable resource for understanding the state of simulation technology and its applications in verifying digital systems.

Dubey [12] [14] contributes to the understanding of hardware description languages and embedded system design using FPGAs, providing detailed explanations and practical examples. His work is instrumental for designers looking to leverage FPGAs in embedded systems. Arunmozhi and Mohan [13] explore the implementation of digital image processing algorithms on FPGAs using hardware description languages, demonstrating the practical application of Verilog and VHDL in specific domains such as image processing.

Areibi [15] and Ratan [17] focus on educational and specialized applications of digital design, with Areibi discussing a first course in digital design using VHDL and programmable logic, and Ratan exploring the design of phase-locked loops for high-speed serial link applications. These works are essential for educators and specialists looking to deepen their understanding of specific digital design challenges. Finally, Derickson and Müller [16] offer a comprehensive guide to digital communications test and measurement, providing critical insights into the physical layer characterization of high-speed digital systems. Their work is invaluable for those involved in the testing and measurement of high-performance digital communications systems.

This review highlights the breadth and depth of literature available on digital system design using Verilog and related technologies, encompassing both foundational texts and advanced research across various applications. Each of these works contributes to a comprehensive understanding of digital design, from basic principles to cutting-edge applications in high-speed systems.

#### 3. Methodology

The methodology for the digital system design process using Verilog, as outlined in the context of high-speed applications, involves a systematic approach that integrates theoretical knowledge, practical tools, and iterative testing. This approach ensures that the final digital system meets the desired specifications in terms of performance, reliability, and efficiency.

#### 1. System Specification and Requirements Analysis

The first step in the methodology is to clearly define the system specifications and requirements. This involves understanding the functional requirements, performance goals, power constraints, and interface protocols that the digital system must adhere to. Key performance metrics such as speed, latency, power consumption, and area utilization are determined at this stage. The design process begins with a comprehensive analysis of these requirements to establish a clear roadmap for the subsequent design phases.

#### 2. Design Conceptualization and Architectural Planning

With the system requirements defined, the next step is to conceptualize the design and plan the architecture. This includes selecting the appropriate digital logic components, determining the data flow, and defining the control logic. The architecture is designed to optimize performance metrics while considering trade-offs such as speed versus power consumption or area versus performance. High-level models may be created using block diagrams to represent the major components and their interactions.

Design Conceptualization and Architectural Planning is a critical phase in the digital system design process, where the high-level structure of the system is defined and the roadmap for detailed implementation is established. This stage involves translating system specifications and requirements into a functional architecture that will guide the subsequent design and development phases. The effectiveness of this phase directly impacts the performance, efficiency, and scalability of the final digital system.

#### **Understanding System Requirements**

The process begins with a deep understanding of the system requirements, which include functional specifications, performance targets (such as speed, latency, and power consumption), and constraints related to cost, area, and technology. These requirements are typically derived from the end application's needs, whether it be a consumer electronics device, a communication system, or an industrial control system. A thorough analysis of these requirements helps in identifying the key components and subsystems that need to be developed.

#### **Defining the System Architecture**

Once the requirements are clearly understood, the next step is to define the system architecture. This involves selecting the appropriate architectural style, which could range from a simple combinational logic circuit to a more complex pipelined or parallel processing architecture. The choice of architecture is influenced by factors such as the required data throughput, processing speed, and the nature of the tasks that the system must perform. For instance, in high-speed digital systems, a pipelined architecture might be chosen to enhance throughput by overlapping the execution of multiple instructions. Similarly, parallelism might be introduced to allow multiple operations to occur simultaneously, thereby increasing performance. The architecture also defines how data will flow through the system, how different modules will interact, and how control signals will be managed.

#### **Component Selection and Integration**

At this stage, the designer selects the individual components that will make up the system. These components include logic gates, flip-flops, multiplexers, arithmetic units, and memory elements. The selection is guided by the need to optimize the system's performance while adhering to constraints such as power consumption and area. The designer must also consider the technology platform, such as FPGA or ASIC, on which the system will be implemented, as this influences component selection and integration.

Component integration is a critical aspect of architectural planning. The designer must ensure that all components work together seamlessly to perform the desired operations. This involves defining clear interfaces between components, specifying the timing relationships, and ensuring that data is correctly synchronized as it moves through the system. In high-speed designs, particular attention must be paid to timing issues, such as clock skew and setup/hold times, which can affect the overall performance of the system.

#### **Trade-offs and Optimization**

Architectural planning often involves making trade-offs between conflicting requirements. For example, increasing the clock speed can improve performance but may lead to higher power consumption and greater heat dissipation. Similarly, reducing area might require the use of more compact, but potentially slower, components. The designer must carefully balance these trade-offs to achieve the optimal design for the given application.

Optimization techniques such as pipelining, parallel processing, and resource sharing are often employed to enhance performance while minimizing resource usage. The goal is to create an architecture that meets all critical performance metrics within the given constraints.

#### High-Level Modeling and Validation

Before moving to the detailed design, it is often beneficial to create high-level models of the architecture using tools such as block diagrams or hardware description languages (HDLs) like Verilog. These models allow for early validation of the design concept, enabling the designer to simulate the system's behavior and identify potential issues. High-level modeling provides a platform for testing different architectural options and making informed decisions about the final design. Design Conceptualization and Architectural Planning is a foundational step that shapes the entire digital system design process. By carefully defining the system architecture, selecting and integrating components, and making informed trade-offs, designers can create efficient, high-performance digital systems that meet the stringent demands of modern applications. This phase sets the stage for successful implementation, ensuring that the design process is both focused and efficient.

Figure 1: Design Architecture

#### 3. Hardware Description Using Verilog

The core of the methodology involves translating the architectural design into a hardware description using Verilog. This step requires writing Verilog code that accurately represents the digital logic at various levels of abstraction—behavioral, register-transfer level (RTL), and gate level. The Verilog code is modularized to improve readability, reusability, and maintainability. Special attention is given to coding practices that optimize for synthesis, ensuring that the resulting hardware meets the desired performance and area constraints.

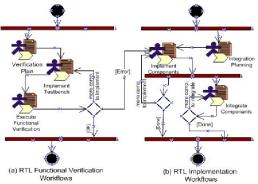

#### 4. Simulation and Functional Verification

Once the Verilog code is developed, it undergoes extensive simulation to verify its functionality. Simulation tools are used to run testbenches that mimic real-world operating conditions. This step ensures that the design behaves as expected under various scenarios, including edge cases and stress conditions. Functional verification is crucial to identifying and correcting errors early in the design process, reducing the likelihood of costly issues later.

Figure 2: Simulation and functional verification

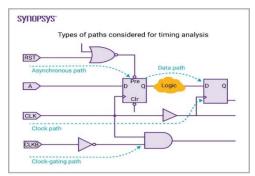

#### 5. Synthesis and Timing Analysis

After successful simulation, the Verilog code is synthesized into a gate-level netlist using a synthesis tool. This netlist represents the physical implementation of the design. Timing analysis is performed to ensure that all timing constraints, such as setup and hold times, are met. Any timing violations are addressed through design optimizations, such as pipelining or retiming.

Figure 3: Path for timing

#### 6. Physical Design and Implementation

The gate-level netlist is then mapped to a target hardware platform, such as an FPGA or ASIC. Physical design steps include placement, routing, and power analysis. The design is optimized for speed, power, and area during these steps to ensure that it meets the system specifications.

#### 7. Post-Implementation Verification and Testing

The final stage involves post-implementation verification, where the design is tested on actual hardware to validate its performance in a real environment. This includes timing closure, signal integrity checks, and power measurement. If any issues are detected, iterative adjustments are made to the design.

This systematic methodology ensures that the digital system design is robust, efficient, and meets the high-speed application requirements.

#### 4. Discussion

The methodology outlined for digital system design using Verilog reflects a comprehensive and structured approach that is essential for developing high-performance, reliable systems. By beginning with a thorough analysis of system specifications and requirements, the methodology ensures that the design is aligned with the intended application's goals from the outset. This careful planning is critical, especially in high-speed digital systems where performance parameters such as latency, throughput, and power efficiency are tightly constrained. The use of Verilog as the primary hardware description language offers significant advantages in the design process. Verilog's ability to model digital systems at various levels of abstraction—ranging from high-level behavioral descriptions to detailed gate-level implementations—provides flexibility and precision. This enables designers to optimize their systems effectively, balancing trade-offs such as speed versus power consumption or complexity versus area utilization. Furthermore, the modular nature of Verilog code supports reusability and maintainability, which are important for managing the increasing complexity of digital systems.

Simulation and functional verification play a crucial role in this methodology. By rigorously testing the design under a variety of scenarios before synthesis, the likelihood of encountering functional errors in later stages is significantly reduced. This not only saves time and resources but also ensures that the final design is robust and performs reliably in real-world conditions. The use of synthesis and timing analysis tools further aids in achieving the desired performance by identifying and correcting timing issues that could affect the system's operation.

Physical design and post-implementation testing are critical for ensuring that the theoretical design performs as expected when mapped to actual hardware. These stages address practical concerns such as placement, routing, power distribution, and signal integrity, which are often the sources of performance bottlenecks in high-speed systems. The iterative nature of the methodology, where issues detected during post-implementation testing led to further refinements, underscores the importance of flexibility and adaptability in the design process.

#### 5. Conclusion

The systematic methodology for digital system design using Verilog, as discussed, is a robust framework that effectively addresses the challenges of developing high-speed applications. By integrating detailed planning, rigorous verification, and iterative refinement, this approach ensures that the final digital system meets stringent performance, power, and reliability requirements. The use of Verilog as a versatile hardware description

language allows for precise and efficient modeling of complex systems, facilitating optimization at both the design and implementation stages.

Through careful attention to each phase of the design process—from initial specification to post-implementation testing—the methodology provides a clear path for creating digital systems that are not only functional but also optimized for real-world performance. This approach is particularly valuable in today's technological landscape, where the demand for faster, more efficient, and reliable digital systems continues to grow. As digital technology advances, the principles and practices outlined in this methodology will remain fundamental to successful digital system design, ensuring that engineers can meet the evolving demands of high-speed applications.

#### References

- [1]. Palnitkar, S. (2003). Verilog HDL: a guide to digital design and synthesis (Vol. 1). Prentice Hall Professional.

- [2]. Ashenden, P. J. (2007). Digital design (verilog): An embedded systems approach using verilog. Elsevier.

- [3]. Khan, S. A. (2011). Digital design of signal processing systems: a practical approach. John Wiley & Sons.

- [4]. Rafiquzzaman, M. (2005). Fundamentals of digital logic and microcomputer design. John Wiley & Sons.

- [5]. Wilson, P. (2015). Design recipes for FPGAs: using Verilog and VHDL. Newnes.

- [6]. Ferdjallah, M. (2011). Introduction to digital systems: modeling, synthesis, and simulation using VHDL. John Wiley & Sons.

- [7]. Ahmad, R., Sidek, O., Hassin, H. W., & Husain, A. S. (2011). Verilog-based design and implementation of digital transmitter for Zigbee applications. International Journal of Emerging Sciences, 1(4), 723.

- [8]. Salcic, Z., & Smailagic, A. (2007). Digital systems design and prototyping: using field programmable logic and hardware description languages. Springer Science & Business Media.

- [9]. Agrawal, R. K., & Mishra, V. R. (2013, April). The design of high speed UART. In 2013 IEEE Conference on Information & Communication Technologies (pp. 388-390). IEEE.

- [10]. Sharawi, M. S., & Aloi, D. N. (2005). Circuit modeling in high-speed designs. IEEE Potentials, 24(1), 17-20.

- [11]. Tan, T. S., & Rosdi, B. A. (2014). Verilog hdl simulator technology: a survey. Journal of Electronic Testing, 30, 255-269.

- [12]. Dubey, R. (2009). Hardware description language: Verilog. Introduction to Embedded System Design Using Field Programmable Gate Arrays, 17-51.

- [13]. Arunmozhi, R., & Mohan, G. (2012). Implementation of digital image morphological algorithm on FPGA using hardware description languages. International Journal of Computer Applications, 57(5).

- [14]. Dubey, R. (2008). Introduction to embedded system design using field programmable gate arrays. Springer Science & Business Media.

- [15]. Areibi, S. (2001, October). A first course in digital design using VHDL and programmable logic. In 31st Annual Frontiers in Education Conference. Impact on Engineering and Science Education. Conference Proceedings (Cat. No. 01CH37193) (Vol. 1, pp. TIC-19). IEEE.

- [16]. Derickson, D., & Müller, M. (2007). Digital communications test and measurement: high-speed physical layer characterization. Pearson Education.

- [17]. Ratan, R. (2014). Design of a phase locked loop based clocking circuit for high speed serial link applications (Doctoral dissertation, University of Illinois at Urbana-Champaign).

- [18]. Siddique, I. M. (2015). Fundamentals and Applications of Network Engineering: A Comprehensive Introduction to Layer-2 Switching and Layer-3 Routing. Journal of Scientific and Engineering Research, 2015, 2(3):51-60.