## Available online www.jsaer.com

Journal of Scientific and Engineering Research, 2024, 11(3):294-297

**Research Article**

ISSN: 2394-2630 CODEN(USA): JSERBR

# **Edge Effects of Voltage Shifters over Nanometer CMOS Power Variations**

## Apoorva Reddy Proddutoori

San Diego

Email: apoorvaproddutoori@gmail.com

Abstract The engineering is planned with multi-limit voltage CMOS strategy. The multi-limit voltage CMOS method is utilized in the plan of voltage level shifter in request to decrease deferral and power. Low-limit voltage gadgets are utilized to decrease deferral and power dissemination is diminished with the utilization of high limit voltage gadgets. In the following paper, the effectiveness of a customary cross-coupled door CMOS span rectifier utilized in MEMS (microelectromechanical framework) piezoelectric energy reapers is examined. Voltage level shifter is a gadget which changes over one voltage level to another. Voltage level shifters are utilized to connect different circuit blocks working at various supply voltages. At the limits of various voltage islands on the framework on-chip (SoC) voltage level shifter is utilized. The outcomes are assessed for ideal burden obstruction, and it is affirmed that a lower limit voltage brings about critical upgrades to the productivity of the rectifier at lower input voltage amplitudes.

Keywords power, Voltage, SoC, level shifter, CMOS

### 1. Introduction

The field effect transistor (FET) operates as a conductive semiconductor channel where the number of charge carriers in the channel is controlled by a gate. The primary application of the MOS system is the metal oxide semiconductor field effect transistor (MOSFET). The use of MOSFETs in integrated circuits was a major development in the implementation of fast and inexpensive digital circuits.

MOSFET, also known as insulated gate FET (IGFET), is widely used as a digital switching element and in LSI and VLSI circuits. In this paper, we study the influence of hot carriers on the threshold voltage of an N-channel MOSFET, operating in linear and saturation modes. We also demonstrate the effect of a short channel length on the device's threshold voltage before and after the hot carrier fails over time under DC stress conditions. To do this, we use a reliability simulation tool, which takes into account the variation in device performance over time due to the continuous degradation mechanism.

Indeed, the simulator has been deployed to reduce the time and cost of accelerated aging tests, which are also very complex. The simulator integrates models of the decomposition mechanism, apparently that of HC. It is applied to MOSFET samples to introduce the variation of device parameters over time. Threshold instability can cause the device to behave differently during static and switching operations. Therefore, it is necessary to study the impact of threshold voltage variation on device operation in power electronic converters.

In an increasing value of the resistance in dynamic state is observed at low gate voltage due to a positive shift of the threshold voltage during transient switching in . The impact of the positive shift of Vth on the crosstalk effect was investigated and it was concluded that the positive shift of Vth helps to minimize crosstalk in fast switching GaN devices.

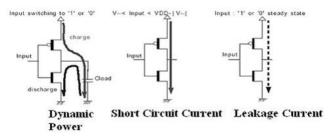

Figure 1: Power

The thyristor based static var compensators (SVCs) made up of fixed capacitors and thyristor-controlled reactors can progressively repay reactive power by controlling its terminating points. Nonetheless, during the activity of low-request symphonious flows are produced, which can disintegrate the framework exhibitions.

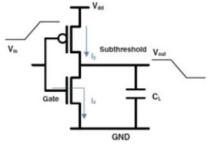

Figure 2: CMOS

The voltage level shifter proposed in employments current generator circuit, which gives current to voltage transformation arrange as it were amid move to decrease inactive control dissemination. In a circuit based on Wilson current reflect has been proposed. The circuit gives inactive control sparing, but the yield of the current reflect isn't steady for higher input. In a voltage level shifter is proposed with restricted speed and moo inactive control utilization. But the voltage change extend is generally less. The plan displayed in is the altered plan of the plan appeared in [1], which has made strides speed and moderately less control utilization. In this paper, wide run voltage level shifter is displayed with diminished delay and moo control utilization.

#### 2. Nm Voltage Shifters

The essential worth which models, describes and mimics the MOSFET is the edge voltage (Vt) which is the base voltage at which the semiconductor turns ON. It is applied at the entryway to cause solid reversal implies that the surface has turned into an electron rich. The limit voltage is otherwise called the turn on voltage which works on the exhibition of the computerized circuits. Voltage limit based cell adjusting works by observing the voltages of individual cells inside a battery pack. At the point when certain cell voltages surpass predefined limits, it are set off to adjust activities. Dynamic adjusting moves charge from high-voltage cells to low-voltage cells, while uninvolved adjusting levels cell voltages utilizing resistors. This technique guarantees that all cells stay inside an ideal voltage range, enhancing the presentation and life span of the battery pack.

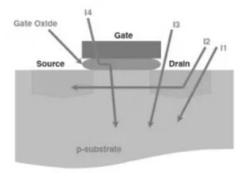

Figure 3: Gate Diagram

Voltage Edge Based Cell Adjusting is a typical procedure utilized in Battery The executives Frameworks to guarantee ideal execution and life span of lithium-particle batteries. This technique includes checking the voltage of every cell inside the battery pack. At the point when a cell comes to a predefined edge voltage, the adjusting hardware enacts to reallocate energy among cells. By moving abundance charge from cheated cells to undercharged ones, Voltage Limit Based Cell Adjusting balances the voltage levels across all cells, forestalling limit uneven characters and drawing out the general battery duration. This cycle is urgent for expanding energy stockpiling limit and keeping up with reliable execution over the long haul. Voltage Limit Based Cell Adjusting assumes an essential part in improving battery productivity and unwavering quality by effectively overseeing cell voltages to forestall undercharging or cheating issues that can prompt untimely corruption.

The paper is built as follows: the positive shift of Vtth subsequent to obstructing the high voltage is first checked tentatively in Area II. Both the test result from the bend tracer and from the proposed Vth estimation circuit are introduced, and the limit voltage shift's impact on the static boundary is assessed. A short time later, a devoted twofold heartbeat test framework with controlled obstructing time on the gadget under test (DUT) is presented in Area III, and the exchanging loss of the DUT is looked at under a short and long obstructing time. Finally, the ends are given summing up the exploratory outcomes. In a multi-facet system, control tracks on each metallization layer run the total pass on and are symmetrical to the tracks in adjacent layers. By implies of clusters at the track crossing focuses relate the tracks in connecting layers. Fig. 2 appears a numerical depiction besides, demonstrate of the vias. Vias are tended to as assurances whose values depend upon their perspectives.

Figure 4: Gate Voltage vs Capacitance

#### 3. Voltage Scaling Analysis

To restrict the power and postpone expansion in later MOS innovation ages supply and edge voltage will need to ceaselessly scale. For accomplishing high return the controlling of edge voltages is fundamental by scaling oxide thickness that further develops limit voltage levels. However a low edge voltage levels are required which can be gotten by scaling the stockpile voltages without influencing the presentation of the gadget. On the off chance that both inventory and edge voltages are downsized the proliferation postponements and power dispersal are decreased at the same time.

Anyway edge voltage scaling is a significant essential concern, it expands Bite the dust-to-pass on, With-kick the bucket boundary varieties, short channel impacts also, sub-edge spillage flows. To decrease the impact of limit scaling on short channel impacts, bite the dust to-bite the dust, inside pass on boundary varieties different methods have been proposed.

Body biasing circuit strategy is utilized to decrease the impact of limit scaling in MOSFETs. By changing the capability of the body terminals the limit voltage of the semiconductors is scaled powerfully. Contingent on the extremity of the possible distinction between the body and the source terminal the Vt can be expanded or diminished.

Converse Body Predisposition - A negative voltage is applied across the source to substrate intersection area to expand the limit voltage. In this procedure, the width of the consumption locale increments which builds the consumption width relates to an expansion in the ionic charge in the semiconductor plate of the MOS capacitor. To support charge balance, the charge in the reversal layer is finished, because of which the door voltage should be improved to accomplish reversal brings about expanded limit voltage. This procedure moreover lessens the varieties in power and speed qualities because of vacillations in kick the bucket to-pass on, supply voltage, temperature boundaries.

Forward Body Predisposition - By applying positive voltage across the source to substrate intersection the limit voltage can be decreased. The width of the consumption district diminishes brings about decline in the ionic charge in the MOS capacitor. To keeping up with charge balance, the charge in the reversal layer increments, as a outcome the door voltage expected to accomplish reversal is diminished. This strategy is more favorable than turn around body inclination procedure to future MOS innovation.

#### 4. Impact of Voltage Benefits

Limit voltage variety can altogether affect the unwavering quality and execution of electronic gadgets. In the event that the limit voltage varieties are not as expected made up for, it can prompt deviations from the ideal working circumstances, bringing about diminished gadget execution and dependability.

For instance, on the off chance that the edge voltage of a semiconductor is surprisingly high, it might require a higher info voltage to turn on, prompting expanded power utilization and decreased productivity. Then again, assuming the edge voltage is lower than anticipated, the gadget might turn on accidentally, causing spillage flows and potential circuit glitches. By carrying out powerful pay methods, the effect of limit voltage varieties can be limited, guaranteeing that the gadgets work dependably and perform ideally.

All in all, limit voltage variety is a basic viewpoint to think about in electronic gadgets. Grasping the wellsprings of variety and carrying out proper remuneration methods is fundamental for guaranteeing dependable and elite execution activity. By tending to edge voltage varieties, fashioners can improve gadget execution and upgrade generally framework unwavering quality.

#### 5. Conclusion

In this paper, the effect of the limit voltage unsteadiness on the exhibition of the p-GaN gadget is contemplated. In particular, a devoted test arrangement is planned which can quantify the limit voltage following impeding the high voltage. From the exploratory outcome, an increment of Vth is noticed in the wake of impeding the high channel to-source voltage. With the guide of the proposed VVtth estimation circuit, a base high voltage beat of 2 μs is applied to the gadget, and it is carved out that the opportunity consistent of the edge voltage increment is inside the scope of a few µs.

#### References

- Md. Mohsinur Rahman Adnan1, Quazi D.M. Khosru, "Effects of uniaxial strain on gate capacitance [1]. and threshold voltage of double gate junctionless transistor", IEEE 13th Nanotechnology Materials and Devices Conference (NMDC), 2018

- J. Sidhakar, A.Mallikarjuna Prasad, Ajit Kumar Panda, "Exhaustive Analysis & Behavior of [2]. Nanometer MOSFET for Threshold Voltage Variations", 3rd International Conference on Signal Processing, Communication and Networking (ICSCN), 2015

- Priti Gosatwar, Ujwala Ghodeswar, "Design of Voltage Level Shifter for Multi-supply Voltage [3]. Design", International Conference on Communication and Signal Processing, 2016

- [4]. Insaf Lahbib, Aziz Doukkali, Patrick Martin, Guy Imbert, Denis Raoulx, "Hot Carrier injection effect on threshold voltage of NMOSFETs", IEEE, 2015

- Xingwen Li, Seyedfakhreddin Nabavi, Lihong Zhang, "Effect of Varying Threshold Voltage on [5]. Efficiency of CMOS Rectifiers for Piezoelectric Energy Harvesting Applications", IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), 2020

- Fei Yang, Chi Xu, Bilal Akin, "Impact of Threshold Voltage Instability on Static and Switching [6]. Performance of GaN Devices with p-GaN Gate", IEEE, 2019

- [7]. https://semiengineering.com/knowledge\_centers/low-power/low-power-design/power-consumption/

- https://www.semaforobares.com/ [8].

- [9]. https://www.redwaypower.com/voltage-threshold-based-cell-balancing-vs-energy-transfer-based-cellbalancing-in-battery-bms/

- [10]. https://www.vishay.com/docs/68214/turnonprocess.pdf